# **STM32F4xx Technical Training**

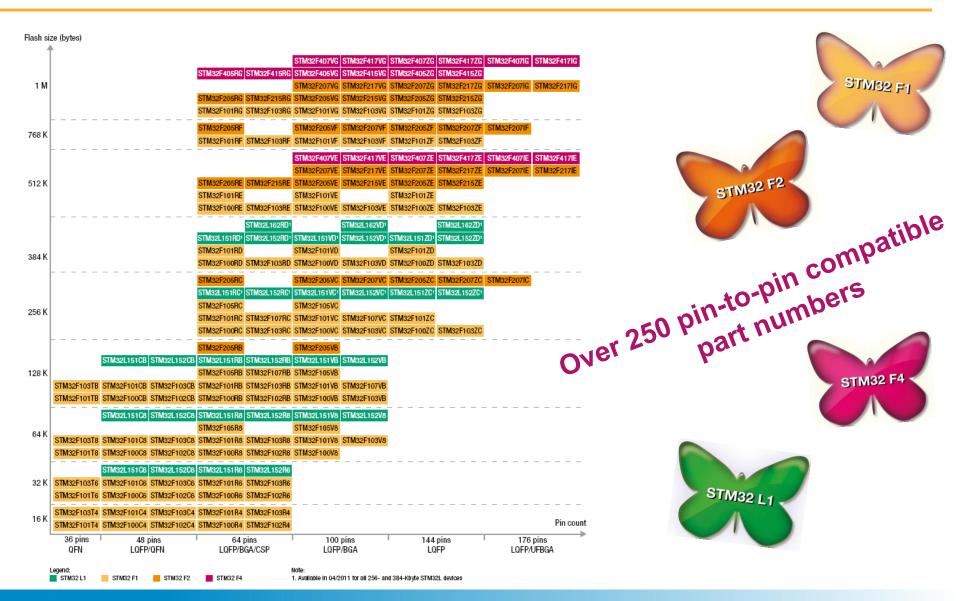

### **4 product series**

Common core peripherals and architecture:

| Comr        | nunication peripherals:<br>USART, SPI, I <sup>2</sup> C                        |

|-------------|--------------------------------------------------------------------------------|

| Multiple    | e general-purpose timers                                                       |

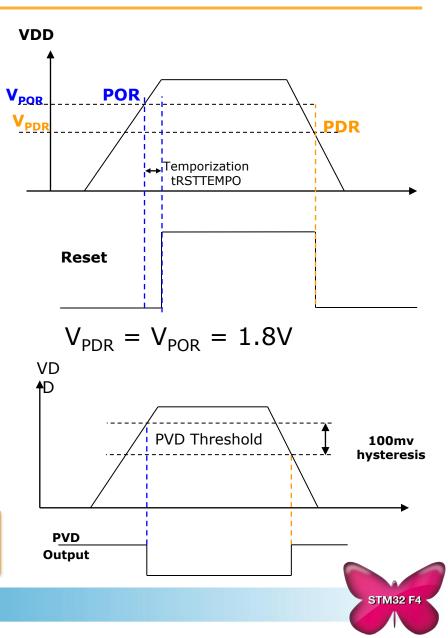

| Integra     | ted reset and brown-out<br>warning                                             |

|             | Multiple DMA                                                                   |

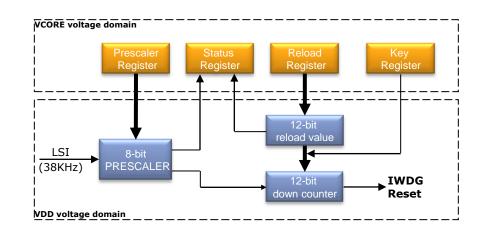

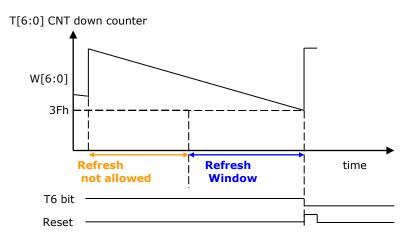

|             | 2x watchdogs<br>Real-time clock                                                |

| lr<br>Pl    | ntegrated regulator<br>LL and clock circuit                                    |

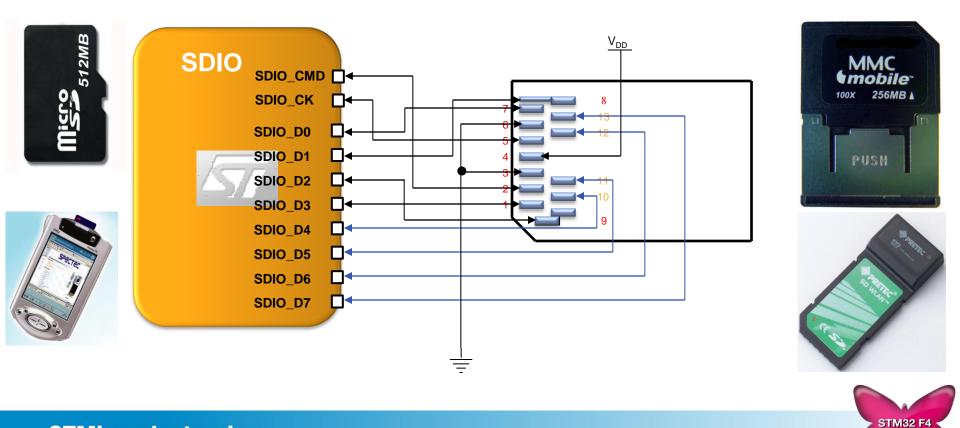

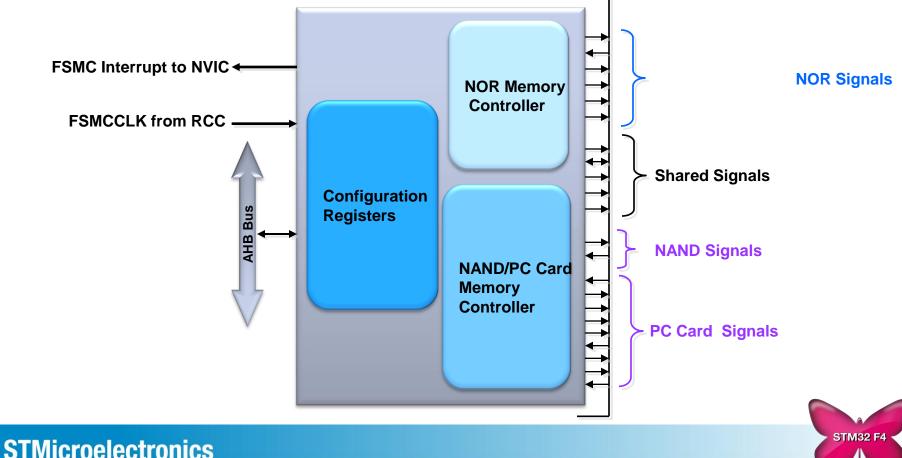

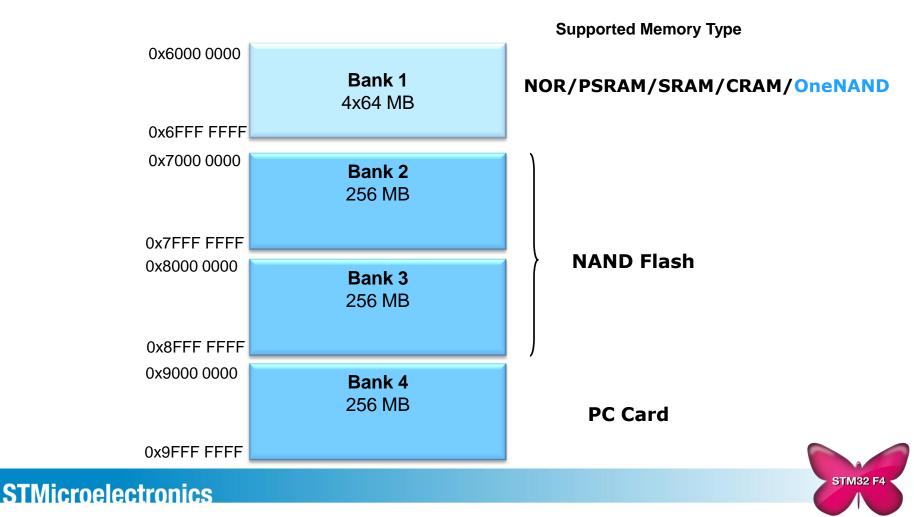

| External    | memory interface (FSMC)                                                        |

|             | Dual 12-bit DAC                                                                |

| Up to 3x    | 12-bit ADC (up to 0.41 µs)                                                     |

| Main osci   | llator and 32 kHz oscillator                                                   |

| Low-speed   | and high-speed internal RC<br>oscillators                                      |

|             | +85 °C and up to 105 °C<br>ting temperature range                              |

| 1.65/1.7 to | voltage 2.0 to 3.6 V or<br>13.6 V (depending on series)<br>5.0 V tolerant I/Os |

| Ť           | emperature sensor                                                              |

| STM32 F4 series - High performance with | DSP (STM32F405/415/407/417) |

|-----------------------------------------|-----------------------------|

|-----------------------------------------|-----------------------------|

| 511415214                                   | series - riigii            | periorinance                | with por to                | 111021 403/413                    | 407/41              | 0                                              |                       | 2.5                                 |

|---------------------------------------------|----------------------------|-----------------------------|----------------------------|-----------------------------------|---------------------|------------------------------------------------|-----------------------|-------------------------------------|

| 168 MHz<br>Cortex-M4<br>with DSP<br>and FPU | Up to<br>192-Kbyte<br>SRAM | Up to<br>1-Mbyte<br>Flash   | 2x USB<br>2.0 OTG<br>FS/HS | 3-phase<br>MC timer               | 2x CAN<br>2.0B      | SDIO<br>2x I²S audio<br>Camera IF              | Ethernet<br>IEEE 1588 | Crypto/hash<br>processor<br>and RNG |

| STM32 F2                                    | series - High              | performance                 | (STM32F20                  | 5/215/207/217                     | )                   |                                                |                       |                                     |

| 120 MHz<br>Cortex-M3<br>CPU                 | Up to<br>128-Kbyte<br>SRAM | Up to<br>1-Mbyte<br>Flash   | 2x USB<br>2.0 OTG<br>FS/HS | 3-phase<br>MC timer               | 2x CAN<br>2.0B      | SDIO<br>2x I <sup>2</sup> S audio<br>Camera IF | Ethernet<br>IEEE 1588 | Crypto/hash<br>processor<br>and RNG |

| TM32 F1                                     | series - Conn              | ectivity line (             | STM32F105                  | /107)                             |                     |                                                |                       |                                     |

| 72 MHz<br>Cortex-M3<br>CPU                  | Up to<br>64-Kbyte<br>SRAM  | Up to<br>256-Kbyte<br>Flash | USB 2.0<br>OTG FS          | 3-phase<br>MC timer               | 2x CAN<br>2.0B      | 2x I <sup>2</sup> S audio                      | Ethernet<br>IEEE 1588 |                                     |

| TM32 F1 :                                   | series - Perfo             | rmance line                 | (STM32F103                 | 3)                                |                     |                                                |                       |                                     |

| 72 MHz<br>Cortex-M3<br>CPU                  | Up to<br>96-Kbyte<br>SRAM  | Up to<br>1-Mbyte<br>Flash   | USB FS<br>device           | 3-phase<br>MC timer               | CAN<br>2.0B         | SDIO<br>2x I <sup>2</sup> S                    |                       |                                     |

| TM32 F1                                     | series - USB               | Access line (S              | STM32F102)                 |                                   |                     |                                                |                       |                                     |

| 48 MHz<br>Cortex-M3<br>CPU                  | Up to<br>16-Kbyte<br>SRAM  | Up to<br>128-Kbyte<br>Flash | USB FS<br>device           |                                   |                     |                                                |                       |                                     |

| TM32 F1                                     | series - Acce              | ss line (STM3               | 32F101)                    |                                   |                     |                                                |                       |                                     |

| 36 MHz<br>Cortex-M3<br>CPU                  | Up to<br>80-Kbyte<br>SRAM  | Up to<br>1-Mbyte<br>Flash   |                            |                                   |                     |                                                |                       |                                     |

| TM32 F1                                     | series - Value             | e line (STM32               | F100)                      |                                   |                     |                                                |                       |                                     |

| 24 MHz<br>Cortex-M3<br>CPU                  | Up to<br>32-Kbyte<br>SRAM  | Up to<br>512-Kbyte<br>Flash | 3-phase<br>MC timer        | CEC                               |                     |                                                |                       |                                     |

| STM32 L1                                    | series - Ultra-            | low-power (                 | STM32F151                  | /152)                             |                     |                                                |                       |                                     |

| 32 MHz<br>Cortex-M3<br>CPU                  | Up to<br>48-Kbyte<br>SRAM  | Up to<br>384-Kbyte<br>Flash | USB FS<br>device           | Data EEPROM<br>up to<br>12 Kbytes | LCD<br>8x40<br>4x44 | Comparator                                     | BOR<br>MSI<br>VScal   | AES<br>128-bit                      |

## STM32 – leading Cortex-M portfolio

### High-performance Cortex<sup>™</sup>-M4 MCU

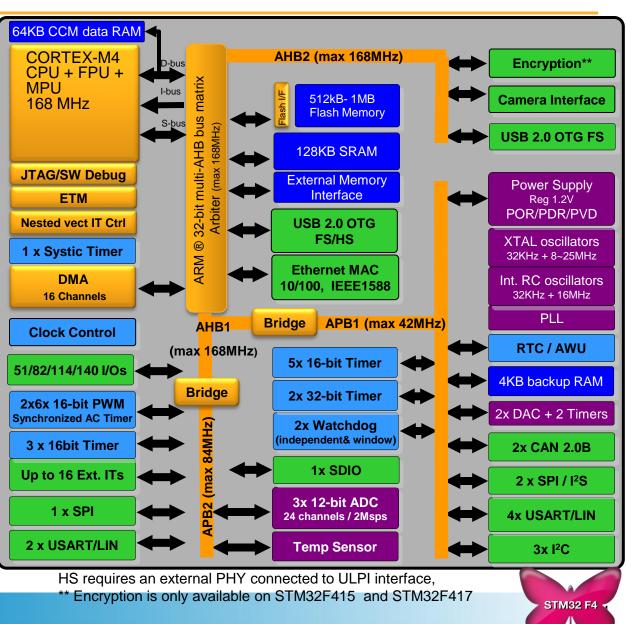

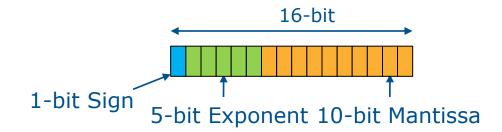

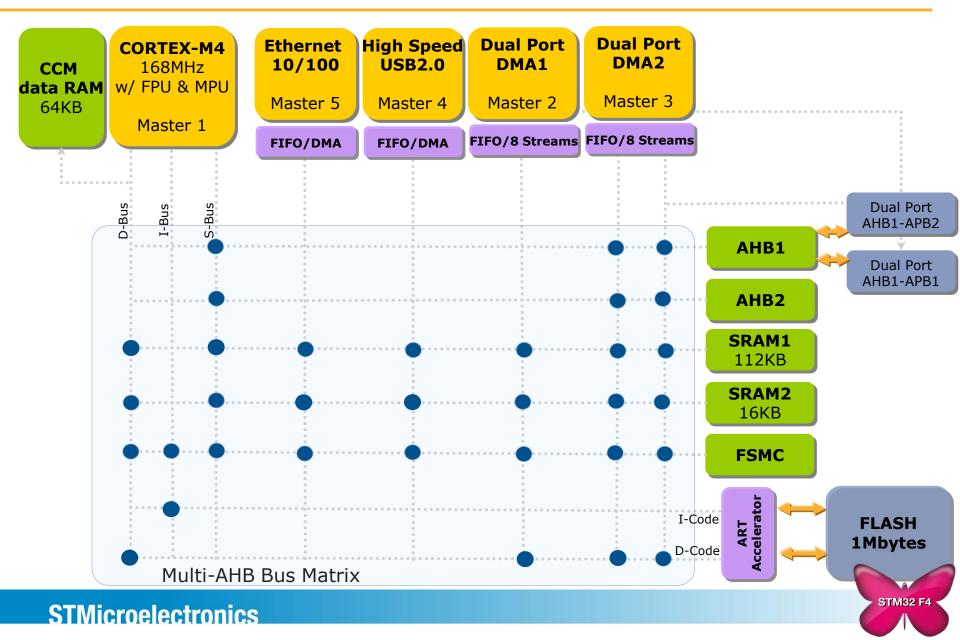

# STM32F4xx Block Diagram

Cortex-M4 w/ FPU, MPU and ETM

- Memory

- Up to 1MB Flash memory

- 192KB RAM (including 64KB CCM data RAM

- FSMC up to 60MHz

- New application specific peripherals

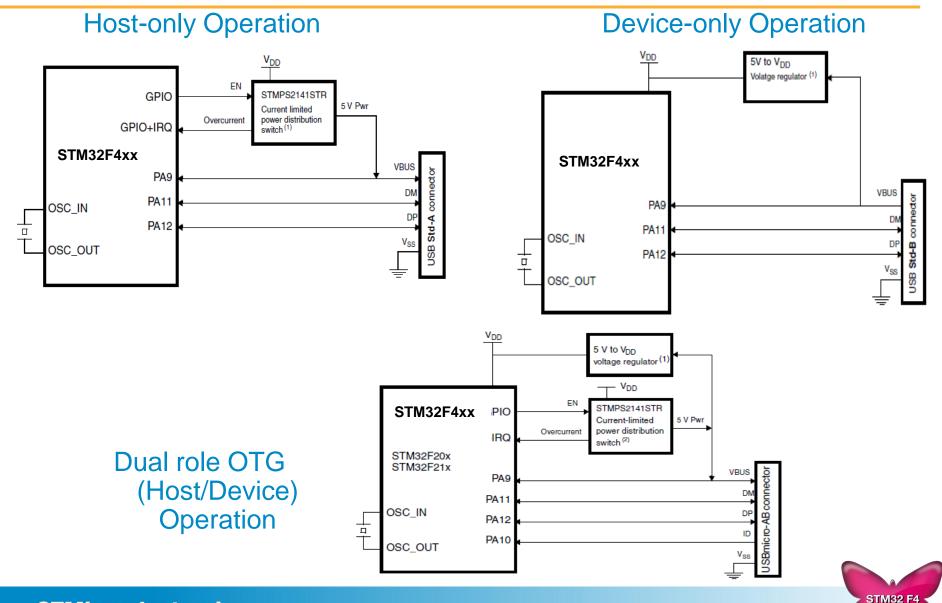

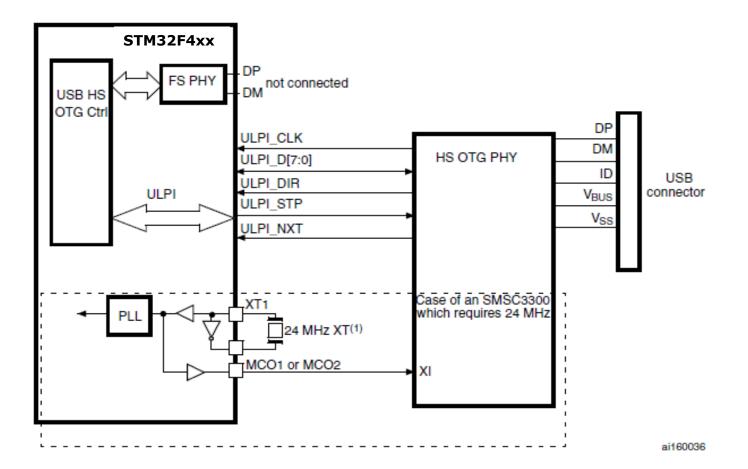

- USB OTG HS w/ ULPI interface

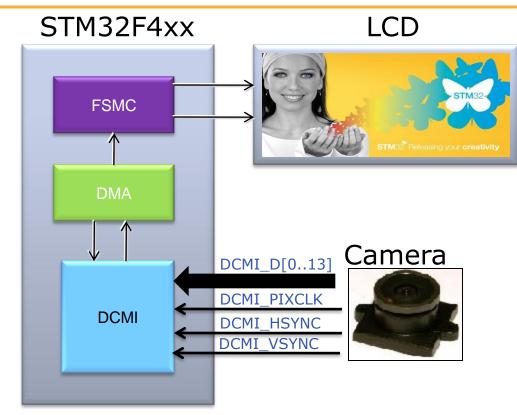

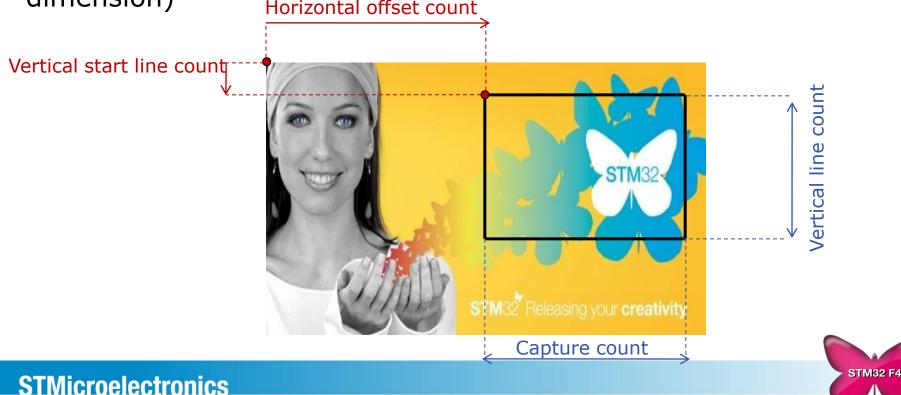

- Camera interface

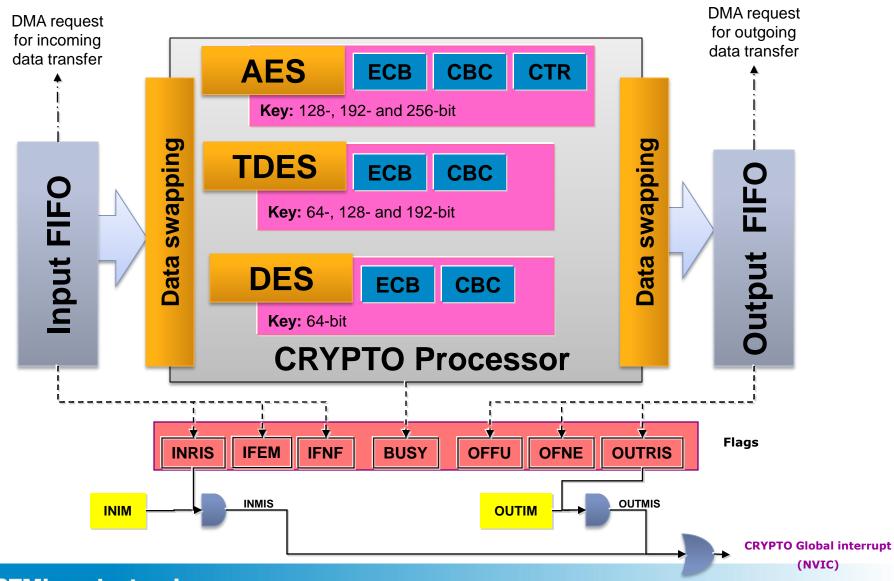

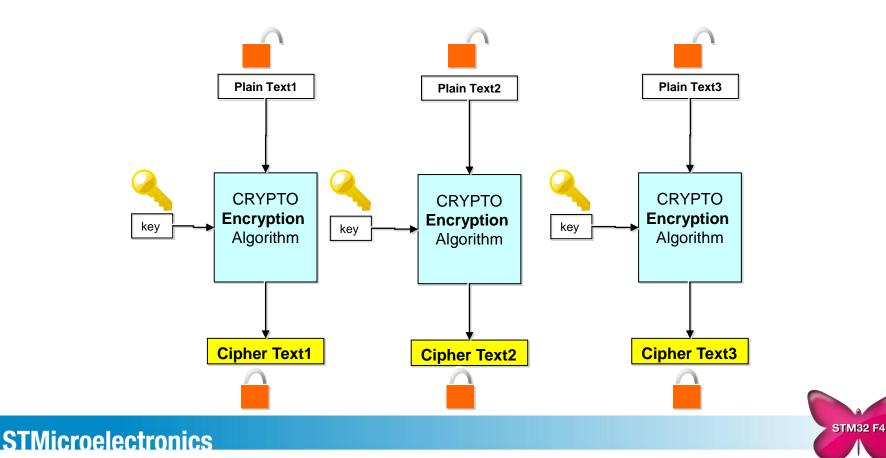

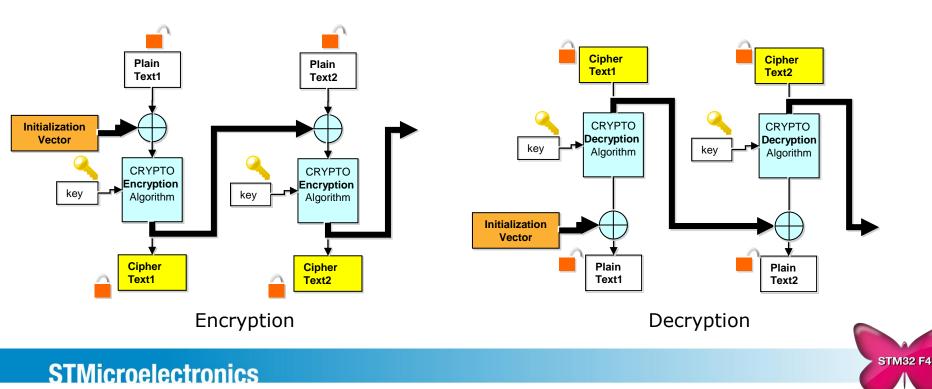

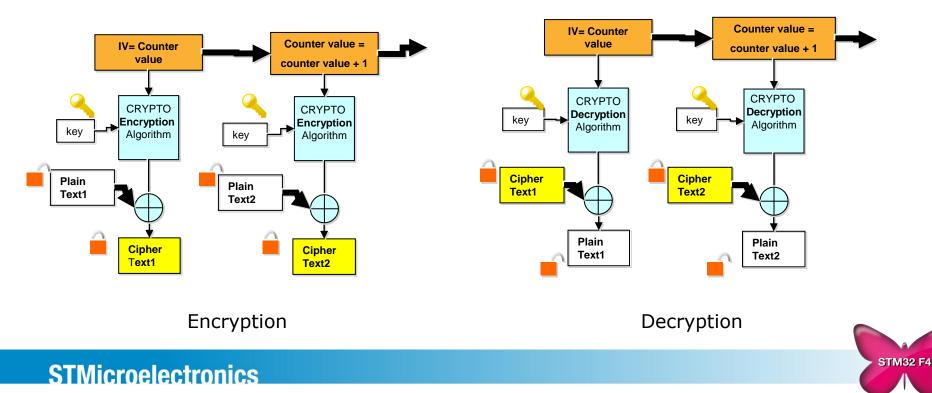

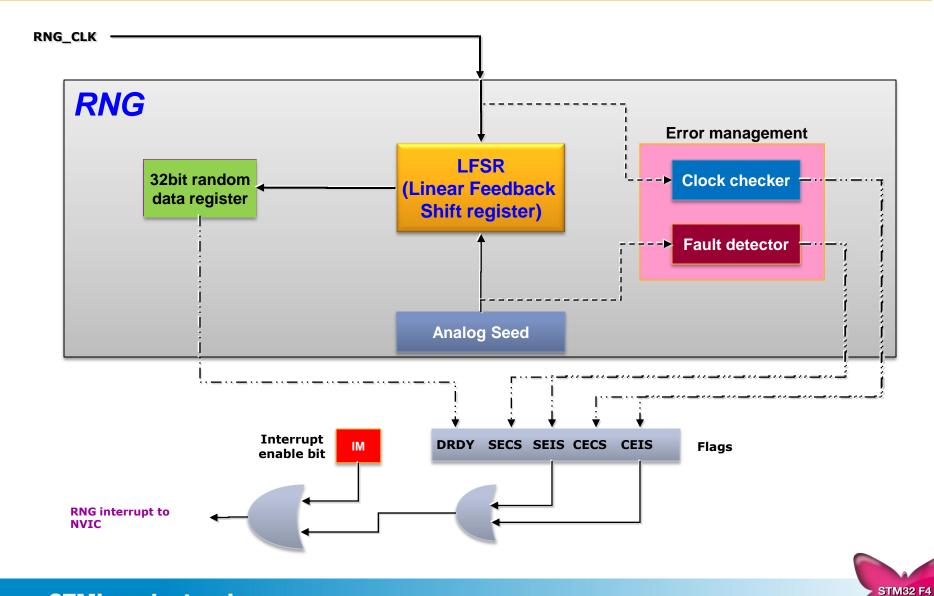

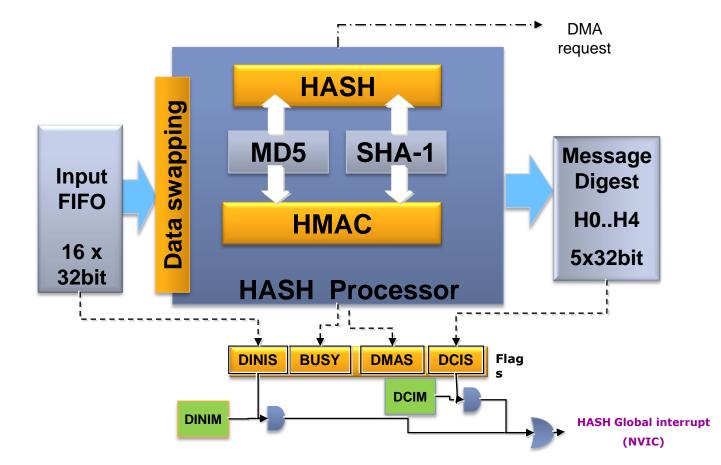

- HW Encryption\*\*: DES, 3DES, AES 256-bit, SHA-1 hash, RNG.

- Enhanced peripherals

- USB OTG Full speed

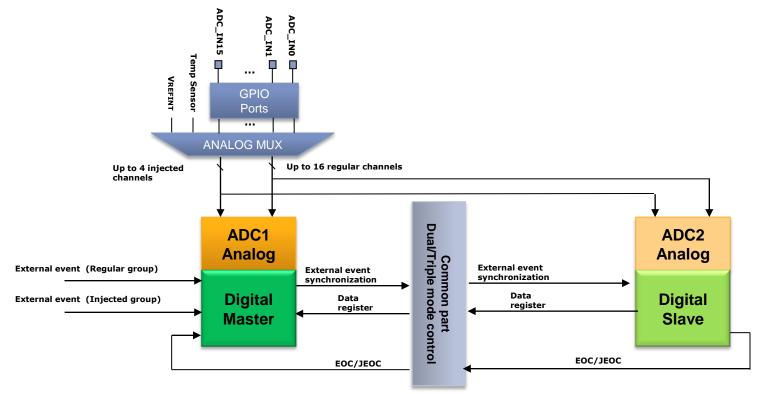

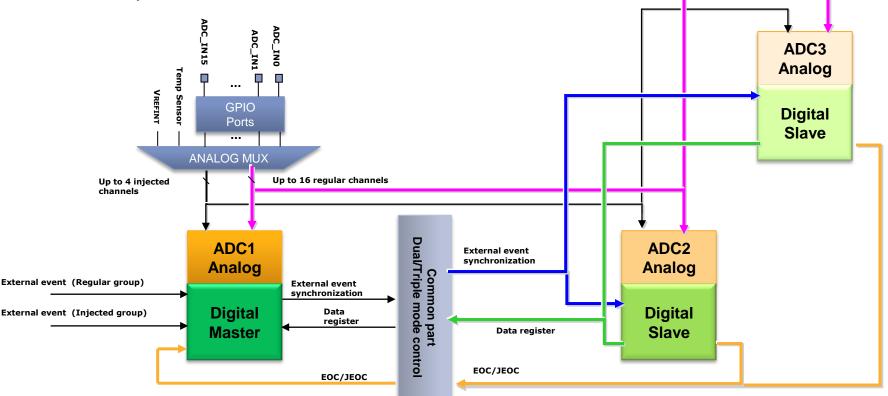

- ADC: 0.416µs conversion/2.4Msps, up to 7.2Msps in interleaved triple mode

- ADC/DAC working down to 1.8V

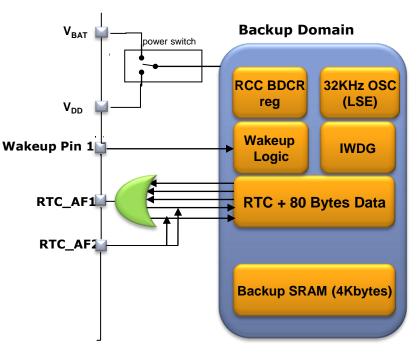

- Dedicated PLL for I<sup>2</sup>S precision

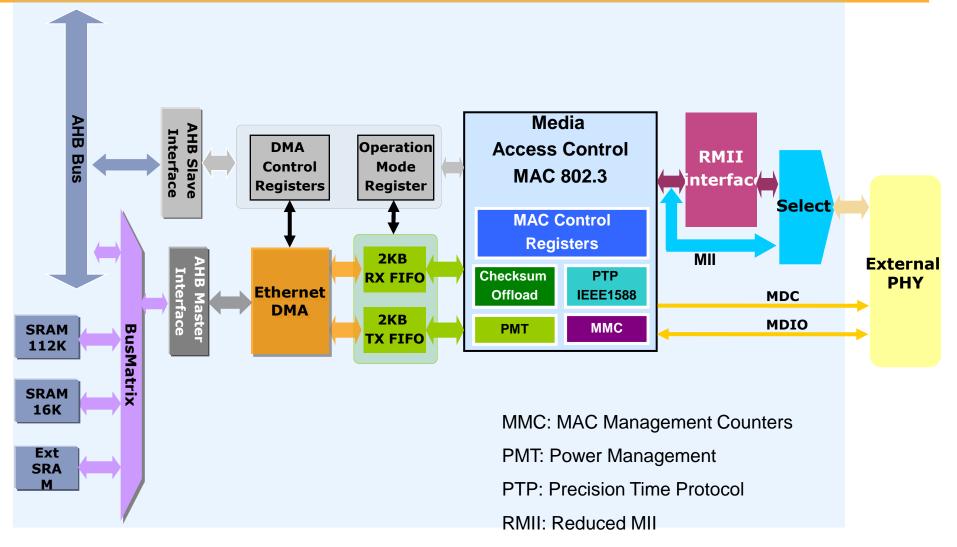

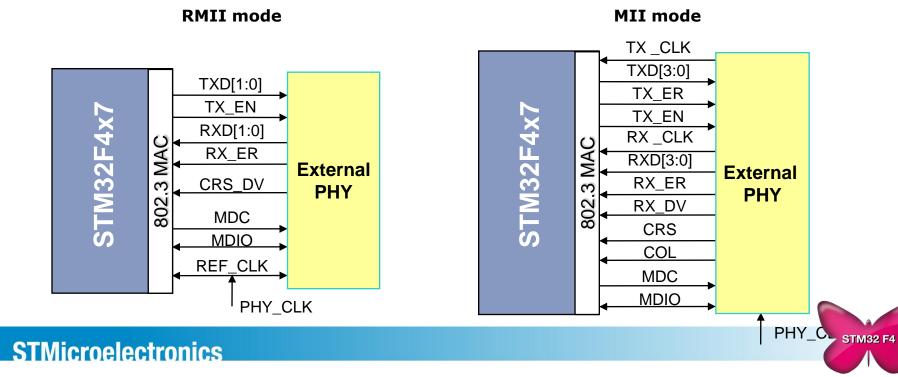

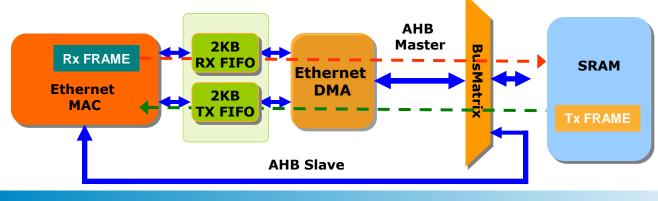

- Ethernet w/ HW IEEE1588 v2.0

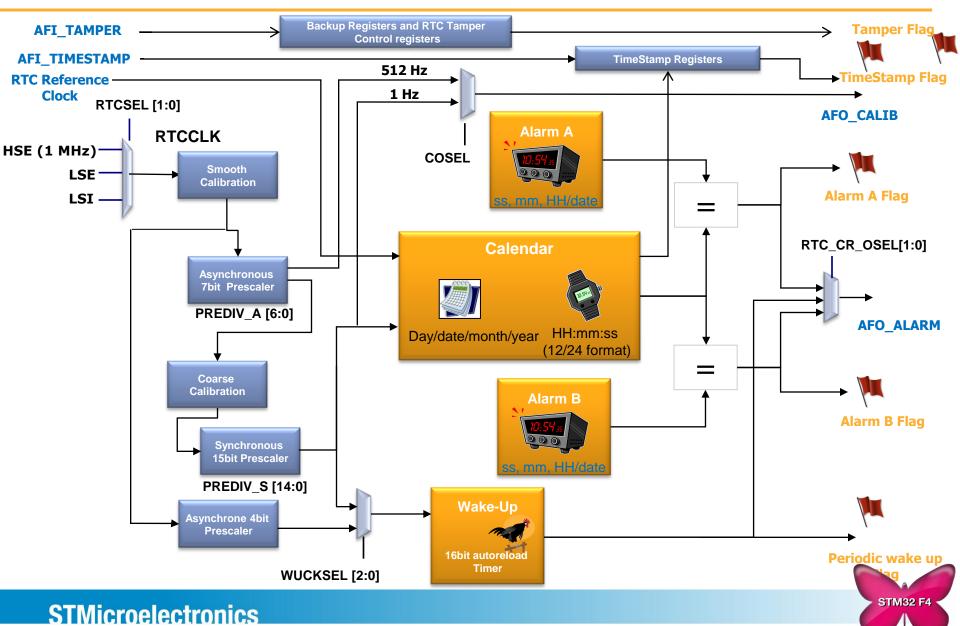

- 32-bit RTC with calendar

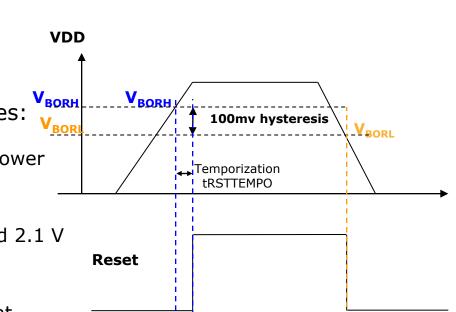

- 4KB backup SRAM in VBAT domain

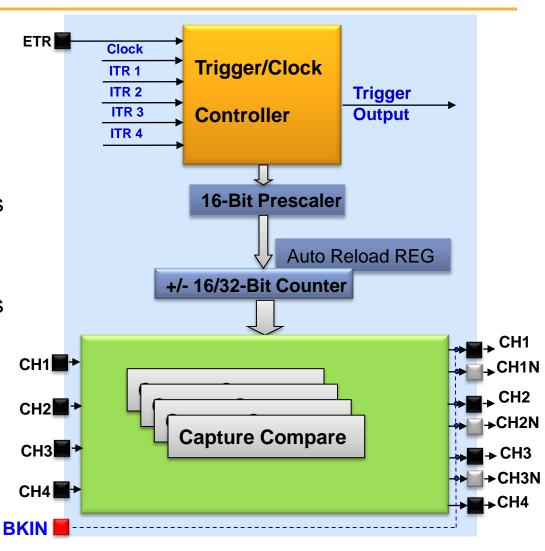

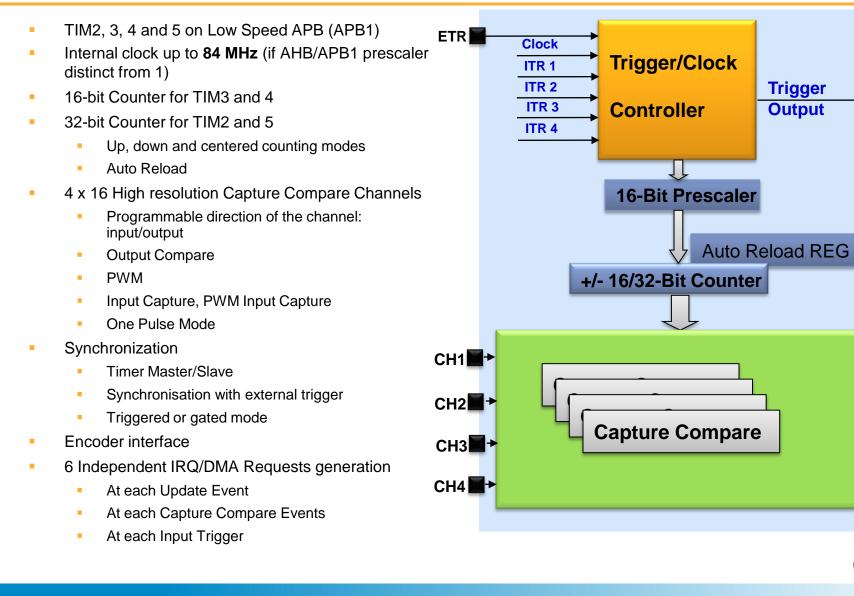

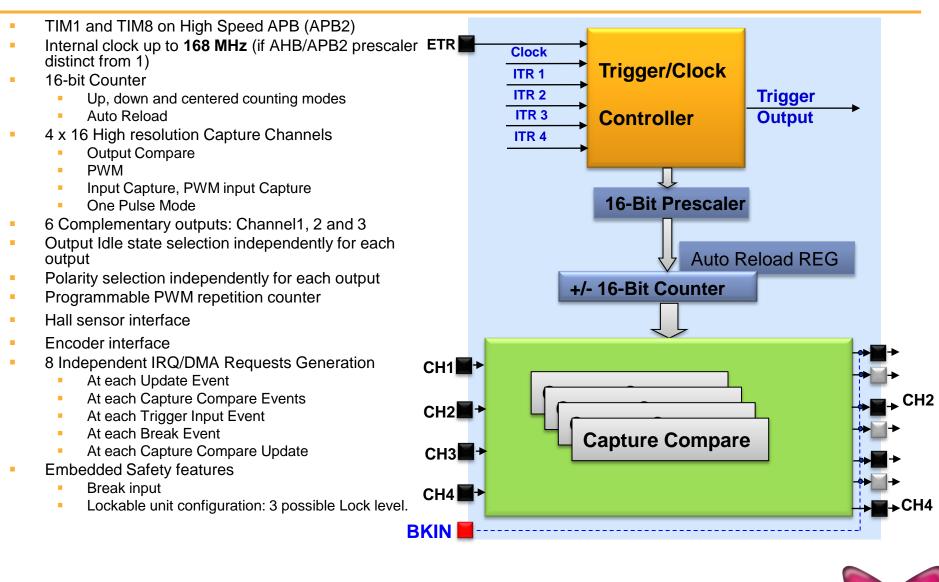

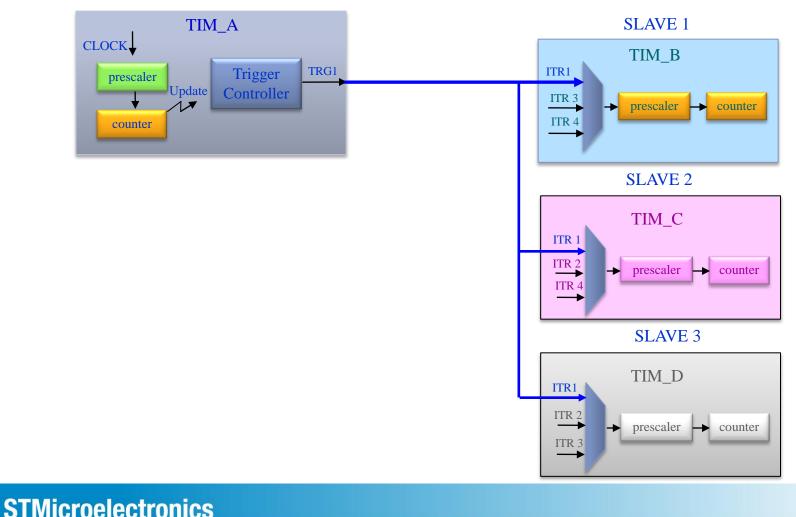

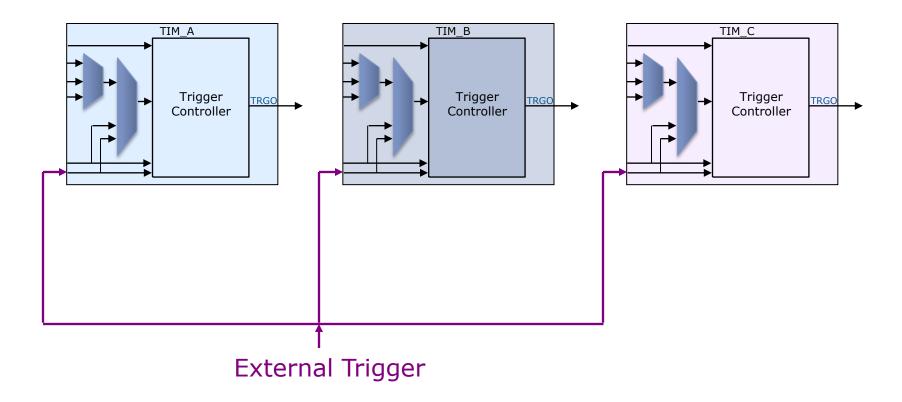

- 2 x 32bit and 8 x 16bit Timers

- high speed USART up to 10.5Mb/s

- high speed SPI up to 37.5Mb/s

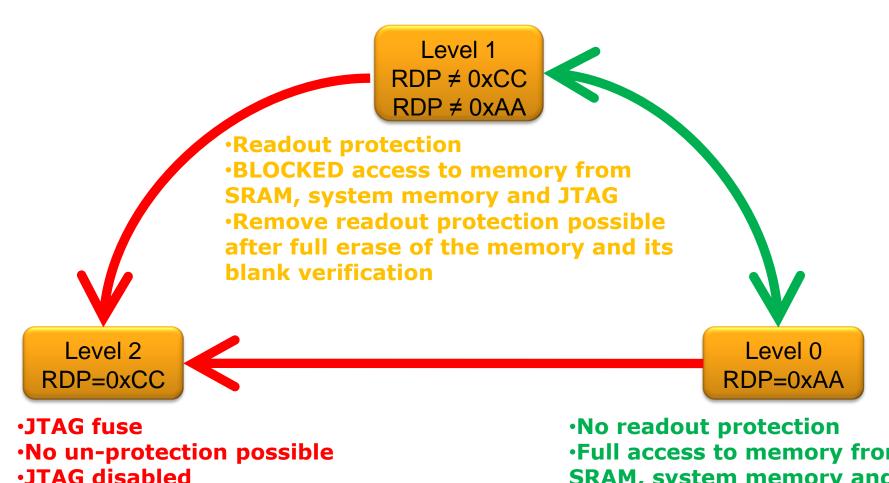

- RDP (JTAG fuse)

- More I/Os in UFBGA 176 package

# STM32F4 Series highlights 1/3

- Based on Cortex M4 core

- The **new DSP and FPU instructions** combined to 168MHz

- Over 30 new part numbers pin-to-pin and software compatible with existing <u>STM32 F2 Series.</u>

### Advanced technology and process from ST:

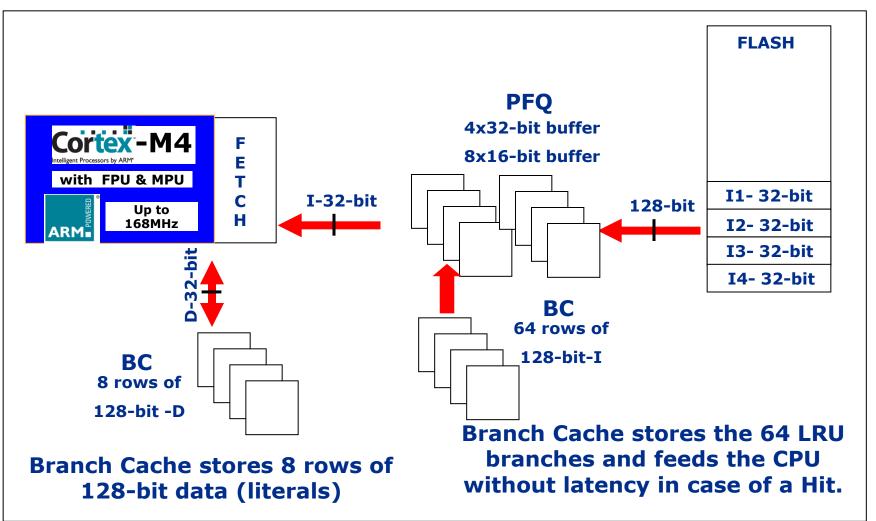

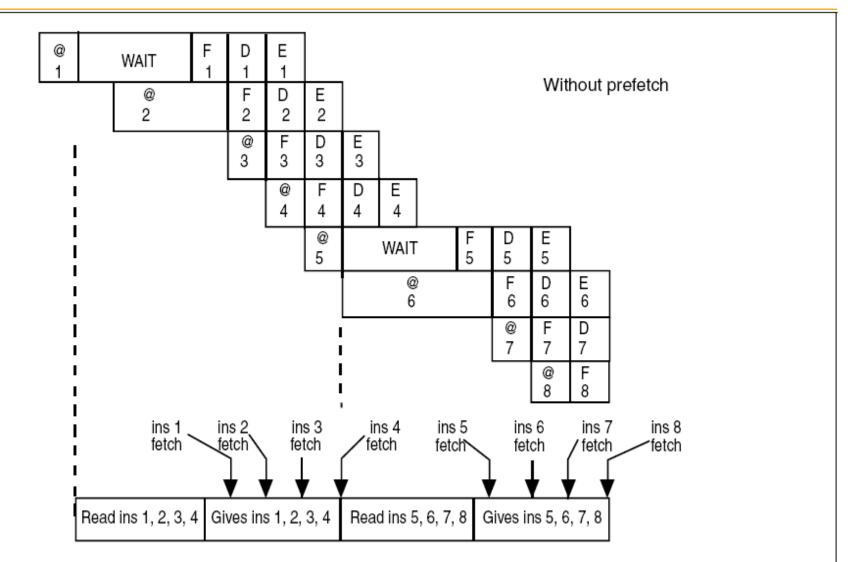

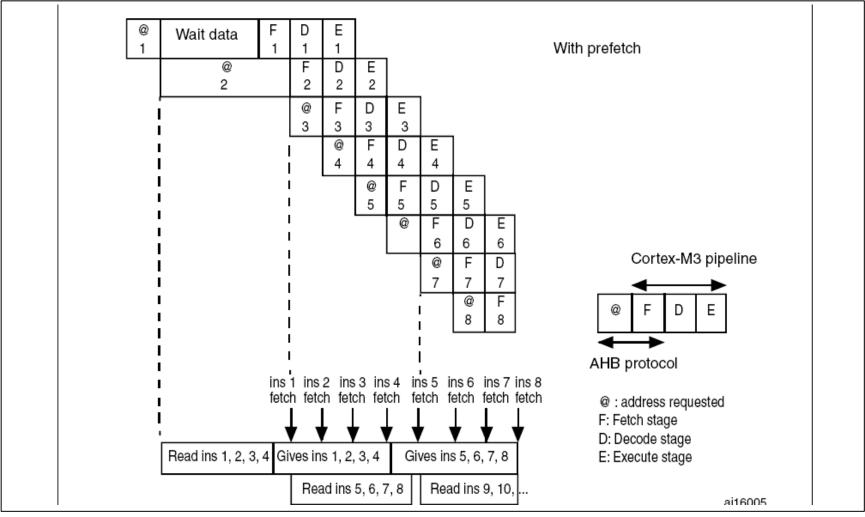

- Memory accelerator: ART Accelerator™

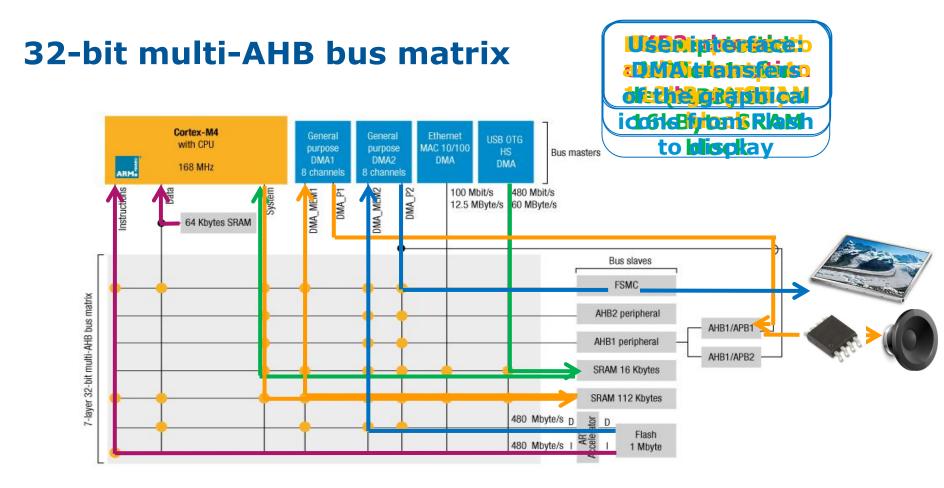

- Multi AHB Bus Matrix

- 90nm process

### **Outstanding results:**

- 210DMIPS at 168MHz.

- Execution from Flash equivalent to 0-wait state performance up to 168MHz thanks to ST ART Accelerator

### More Memory

- Up to 1MB Flash with option to permanent readout protection (JTAG fuse),

- 192kB SRAM: 128kB on bus matrix + 64kB (Core Coupled Memory) on data bus dedicated to the CPU usage

### Advanced peripherals

- USB OTG High speed 480Mbit/s

- Ethernet MAC 10/100 with IEEE1588

- PWM High speed timers: 168MHz max frequency

- Crypto/Hash processor, 32-bit random number generator (RNG)

- 32-bit RTC with calendar: with sub 1 second accuracy, and <1uA</p>

### Further improvements

**STMicroelectronics**

- Low voltage: 1.8V to 3.6V VDD, down to 1.7\*V on most packages

- Full duplex I<sup>2</sup>S peripherals

- **12-bit ADC**: 0.41µs conversion/2.4Msps (**7.2Msps** in interleaved mode)

- High speed USART up to 10.5Mbits/s

- High speed SPI up to 37.5Mbits/s

- Camera interface up to 54MBytes/s

\*external reset circuitry required to support 1.7V

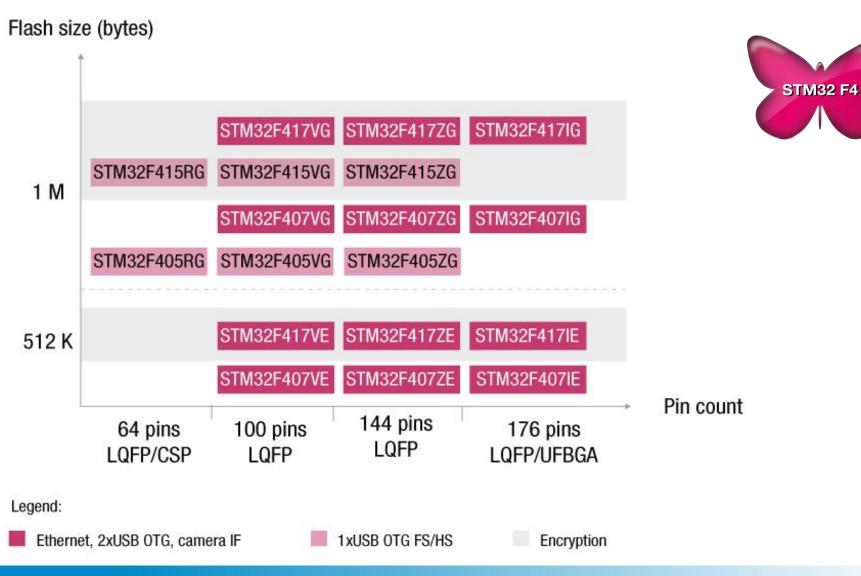

# STM32F4 portfolio

- Evaluation board for full product feature evaluation

- Hardware evaluation platform for all interfaces

- Possible connection to all I/Os and all peripherals

- Discovery kit for cost-effective evaluation and prototyping

- Starter kits from 3<sup>rd</sup> parties available soon

- Large choice of development IDE solutions from the STM32 and ARM ecosystem

STM3240G-EVAL

\$349

STM32F4DISCOVERY

\$14.90

# Tools for development – SW (examples)

#### Commercial ones:

- IAR eval 32kB/30days for test [RK-System]

- Keil (ARM) eval 32kB for test [WG Electronics]

- Based on GCC commercial:

- Atollic Lite (no hex/bin, limited debug), [Kamami]

- Raisonance debug limited to 32kB

- Rowley Crossworks 30 days for test

- Free

- STVP FLASH prog.

- STLink utility FLASH prog. (+cmd line)

- ST FlashLoader FLASH prog.

- Libraries (free)

- Standard peripherals library with CMSIS

- USB device library

| LITE/PRO VERSION FEATORE COMPARISION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| LITE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PRO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| Free                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Low-cost                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |

| Assembler, C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Assembler,<br>C and C++                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |

| <ul> <li>Image: A set of the set of the</li></ul> | <ul> <li>Image: A set of the set of the</li></ul>  |  |  |  |  |  |  |  |  |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <ul> <li>Image: A set of the set of the</li></ul>  |  |  |  |  |  |  |  |  |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ¥                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| <ul> <li>Image: A set of the set of the</li></ul> | <ul> <li>Image: A set of the set of the</li></ul>  |  |  |  |  |  |  |  |  |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <ul> <li>Image: A set of the set of the</li></ul>  |  |  |  |  |  |  |  |  |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <ul> <li>Image: A set of the set of the</li></ul>  |  |  |  |  |  |  |  |  |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| Precompiled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Adaptable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

| ST ST-LINK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Extensive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Available                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

| <ul> <li>Image: A set of the set of the</li></ul> | <ul> <li>Image: A set of the set of the</li></ul>  |  |  |  |  |  |  |  |  |

| <ul> <li>Image: A set of the set of the</li></ul> | <ul> <li>Image: A second s</li></ul> |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | LITE<br>Free<br>Assembler, C<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |

### **ARM Cortex M4 in few words**

# **Cortex-M processors binary compatible**

| РКН    | QADD        | QADD16     | QADD8   | QASX    | QDADD      | QDSUB    | QSAX    | QSUB       |

|--------|-------------|------------|---------|---------|------------|----------|---------|------------|

| QSUB16 | QSUB8       | SADD16     | SADD8   | SASX    | SEL        | SHADD16  | SHADD8  | SHASX      |

| SHSAX  | SHSUB16     | SHSUB8     | SMLABB  | SMLABT  | SMLATB     | SMLATT   | SMLAD   | SMLALBB    |

|        |             |            |         |         |            |          | SMLALBT | SMLALTB    |

| ADC    | ADD         | ADR        | AND     | ASR     | <b>B</b> ( | CLZ      | SMLALTT | SMLALD     |

| BFC    | BFI         | BIC        | CDP     | CLREX   | CBNZ CBZ ( | CMN      | SMLAWB  | SMLAWT     |

| СМР    |             |            | (       | DBG     | EOR        | LDC      | SMLSD   | SMLSLD     |

| LDMIA  | BKPT BLX    | ADC ADD    | ADR     | LDMDB   | LDR        | LDRB     | SMMLA   | SMMLS      |

| LDRBT  | BX CPS      | AND ASR    |         | LDRD    | LDREX      | LDREXB   | SMMUL   | SMUAD      |

| LDREXH | DMB         | BL         | BIC     | LDRH    |            | LDRSB    | SMULBB  | SMULBT     |

| LDRSBT | DSB         | CMN CMP    | EOR     | LDRSHT  | LDRSH      | LDRT     | SMULTB  | SMULTT     |

| MCR    | ISB         | LDR LDRB   |         | LSL     | LSR        | MLS      | SMULWB  | SMULWT     |

| MCRR   | MRS         | LDRH LDRSB | (LDRSH) | MLA     | MOV        | MOVT     | SMUSD   | SSAT16     |

| MRC    | MSR         |            |         | MRRC    | MUL (      | MVN      | SSAX    | SSUB16     |

| NOP    | NOP REV     | MUL MVN    |         | ORN     | ORR        | PLD      | SSUB8   | SXTAB      |

| PLDW   | REV16 REVSH | POP PUSH   |         | PLI     | РОР        | PUSH     | SXTAB16 | SXTAH      |

| RBIT   | SEV SXTB    | RSB SBC    |         | REV     | REV16      | REVSH    | SXTB16  | UADD16     |

| ROR    | SXTH UXTB   | STR STRB   | STRH    | RRX     | RSB (      | SBC      | UADD8   | UASX       |

| SBFX   | UXTH WFE    | SUB SVC    |         | SDIV    | SEV        | SMLAL    | UHADD16 | UHADD8     |

| SMULL  | WFI YIELD   | CORTEX-    | M0/M1   | SSAT    | STC        | STMIA    | UHASX   | UHSAX      |

| STMDB  |             |            |         | STR     | STRB       | STRBT    | UHSUB16 | UHSUB8     |

| STRD   | STREX       | STREXB     | STREXH  | STRH    |            | STRT     | UMAAL   | UQADD16    |

| SUB    | SXTB        | SXTH       | твв     | твн     |            | TST      | UQADD8  | UQASX      |

| UBFX   |             |            |         | USAT    | UXTB       | UXTH     | UQSAX   | UQSUB16    |

|        | WFI (       |            |         |         | C          | ORTEX-M3 | UQSUB8  | USAD8      |

|        |             |            |         |         |            |          | USADA8  | USAT16     |

| USAX   | USUB16      | USUB8      | UXTAB   | UXTAB16 | UXTAH      | UXTB16   |         | Cortex-M4  |

|        |             |            |         |         |            |          |         |            |

| VABS   | VADD        | VCMP       | VCMPE   |         |            |          | VLDM    | VLDR       |

| VMLA   | VMLS        |            | VMRS    | VMSR    |            |          | VNMLA   | VNMLS      |

| VNMUL  | VPOP        | VPUSH      | VSQRT   | VSTM    | VSTR       | VSUB     |         | Cortex-M4F |

|        |             |            |         |         |            |          |         |            |

**STMicroelectronics**

Low-Power Leadership from ARM

## **Cortex-M feature set comparison**

|                               | Cortex-M0                             | Cortex-M3       | Cortex-M4                         |

|-------------------------------|---------------------------------------|-----------------|-----------------------------------|

| Architecture Version          | V6M                                   | v7M             | v7ME                              |

| Instruction set architecture  | Thumb, Thumb-2<br>System Instructions | Thumb + Thumb-2 | Thumb + Thumb-2,<br>DSP, SIMD, FP |

| DMIPS/MHz                     | 0.9                                   | 1.25            | 1.25                              |

| Bus interfaces                | 1                                     | 3               | 3                                 |

| Integrated NVIC               | Yes                                   | Yes             | Yes                               |

| Number interrupts             | 1-32 + NMI                            | 1-240 + NMI     | 1-240 + NMI                       |

| Interrupt priorities          | 4                                     | 8-256           | 8-256                             |

| Breakpoints, Watchpoints      | 4/2/0, 2/1/0                          | 8/4/0, 2/1/0    | 8/4/0, 2/1/0                      |

| Memory Protection Unit (MPU)  | No                                    | Yes (Option)    | Yes (Option)                      |

| Integrated trace option (ETM) | No                                    | Yes (Option)    | Yes (Option)                      |

| Fault Robust Interface        | No                                    | Yes (Option)    | No                                |

| Single Cycle Multiply         | Yes (Option)                          | Yes             | Yes                               |

| Hardware Divide               | No                                    | Yes             | Yes                               |

| WIC Support                   | Yes                                   | Yes             | Yes                               |

| Bit banding support           | No                                    | Yes             | Yes                               |

| Single cycle DSP/SIMD         | No                                    | No              | Yes                               |

| Floating point hardware       | No                                    | No              | Yes                               |

| Bus protocol                  | AHB Lite                              | AHB Lite, APB   | AHB Lite, APB                     |

| CMSIS Support                 | Yes                                   | Yes             | Yes                               |

| STMicroelectronics            |                                       |                 | LO                                |

Low-Power Leadership from ARM

### **Cortex M4**

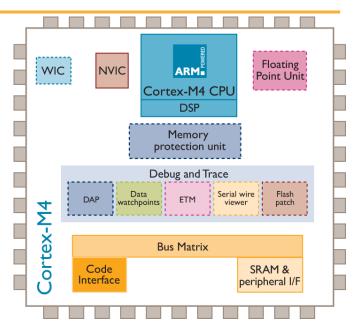

# **Cortex-M4 processor architecture**

#### ARMv7ME Architecture

- Thumb-2 Technology

- DSP and SIMD extensions

- Single cycle MAC (Up to 32 x 32 + 64 -> 64)

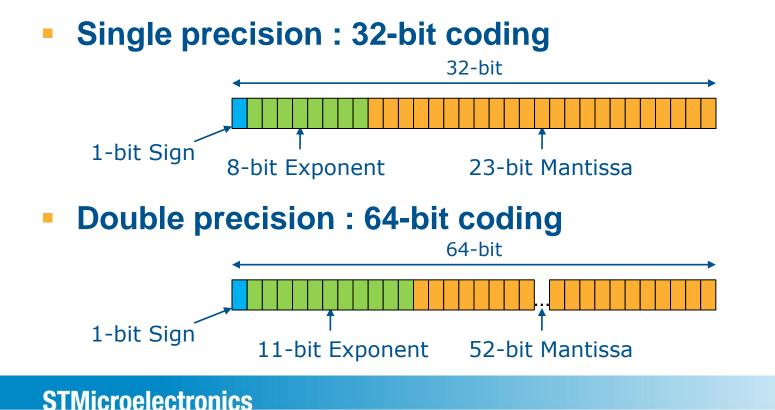

- Optional single precision FPU

- Integrated configurable NVIC

- Compatible with Cortex-M3

#### Microarchitecture

- 3-stage pipeline with branch speculation

- 3x AHB-Lite Bus Interfaces

### Configurable for ultra low power

- Deep Sleep Mode, Wakeup Interrupt Controller

- Power down features for Floating Point Unit

### Flexible configurations for wider applicability

- Configurable Interrupt Controller (1-240 Interrupts and Priorities)

- Optional Memory Protection Unit

- Optional Debug & Trace

- Main Cortex-M4 processor features

- ARMv7-ME architecture revision

- Fully compatible with Cortex-M3 instruction set

- Single-cycle multiply-accumulate (MAC) unit

- Optimized single instruction multiple data (SIMD) instructions

- Saturating arithmetic instructions

- Optional single precision Floating-Point Unit (FPU)

- Hardware Divide (2-12 Cycles), same as Cortex-M3

- Barrel shifter (same as Cortex-M3)

- Hardware divide (same as Cortex-M3)

# Single-cycle multiply-accumulate unit

- The multiplier unit allows any MUL or MAC instructions to be executed in a single cycle

- Signed/Unsigned Multiply

- Signed/Unsigned Multiply-Accumulate

- Signed/Unsigned Multiply-Accumulate Long (64-bit)

- Benefits : Speed improvement vs. Cortex-M3

- 4x for 16-bit MAC (dual 16-bit MAC)

- 2x for 32-bit MAC

- up to 7x for 64-bit MAC

# **Cortex-M4 extended single cycle MAC**

| OPERATION                                     | INSTRUCTIONS                       | CM3 | CM4 |  |

|-----------------------------------------------|------------------------------------|-----|-----|--|

| 16 x 16 = 32                                  | SMULBB, SMULBT, SMULTB, SMULTT     | n/a | 1   |  |

| 16 x 16 + 32 = 32                             | SMLABB, SMLABT, SMLATB, SMLATT     | n/a | 1   |  |

| 16 x 16 + 64 = 64                             | SMLALBB, SMLALBT, SMLALTB, SMLALTT | n/a | 1   |  |

| 16 x 32 = 32                                  | SMULWB, SMULWT                     | n/a | 1   |  |

| $(16 \times 32) + 32 = 32$                    | SMLAWB, SMLAWT                     | n/a | 1   |  |

| (16 x 16) <u>+</u> (16 x 16) = 32             | SMUAD, SMUADX, SMUSD, SMUSDX       | n/a | 1   |  |

| $(16 \times 16) \pm (16 \times 16) + 32 = 32$ | SMLAD, SMLADX, SMLSD, SMLSDX       | n/a | 1   |  |

| $(16 \times 16) \pm (16 \times 16) + 64 = 64$ | SMLALD, SMLALDX, SMLSLD, SMLSLDX   | n/a | 1   |  |

| $32 \times 32 = 32$                           | MUL                                | 1   | 1   |  |

| $32 \pm (32 \times 32) = 32$                  | MLA, MLS                           | 2   | 1   |  |

| $32 \times 32 = 64$                           | SMULL, UMULL                       | 5-7 | 1   |  |

| $(32 \times 32) + 64 = 64$                    | SMLAL, UMLAL                       | 5-7 | 1   |  |

| $(32 \times 32) + 32 + 32 = 64$               | UMAAL                              | n/a | 1   |  |

| 32 <u>+</u> (32 x 32) = 32 (upper)            | SMMLA, SMMLAR, SMMLS, SMMLSR       | n/a | 1   |  |

| (32 x 32) = 32 (upper)                        | SMMUL, SMMULR                      | n/a | 1   |  |

All the above operations are <u>single cycle</u> on the Cortex-M4 processor

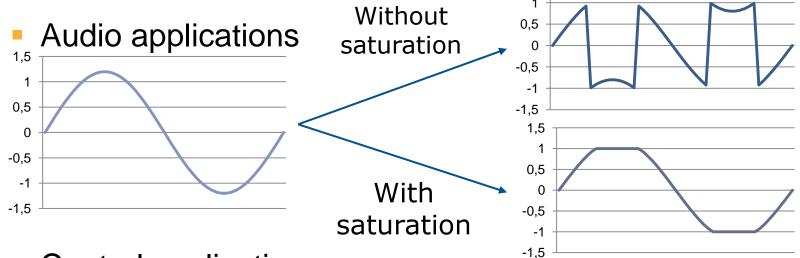

# **Saturated arithmetic**

Low-Power Leadership from ARM

- Intrinsically prevents overflow of variable by clipping to min/max boundaries and remove CPU burden due to software range checks

- Benefits

1,5

- Control applications

- The PID controllers' integral term is continuously accumulated over time. The saturation automatically limits its value and saves several CPU cycles per regulators

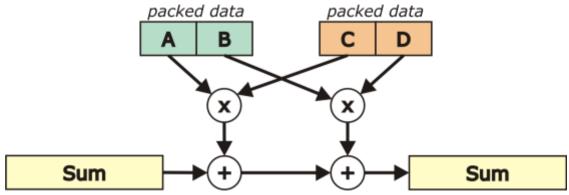

# **Single-cycle SIMD instructions**

- Stands for Single Instruction Multiple Data

- It operates with packed data

- Allows to do simultaneously several operations with 8-bit or 16-bit data format

- i.e.: dual 16-bit MAC (Result = 16x16 + 16x16 + 32)

- Benefits

- Parallelizes operations (2x to 4x speed gain)

- Minimizes the number of Load/Store instruction for exchanges between memory and register file (2 or 4 data transferred at once), if 32-bit is not necessary

- Maximizes register file use (1 register holds 2 or 4 values)

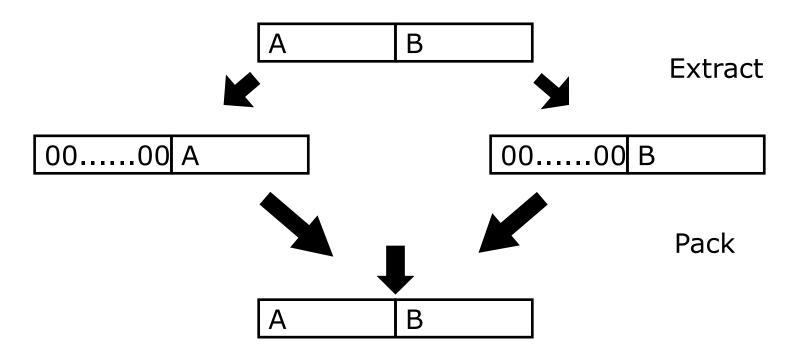

## Packed data types

- Byte or halfword quantities packed into words

- Allows more efficient access to packed structure types

- SIMD instructions can act on packed data

- Instructions to extract and pack data

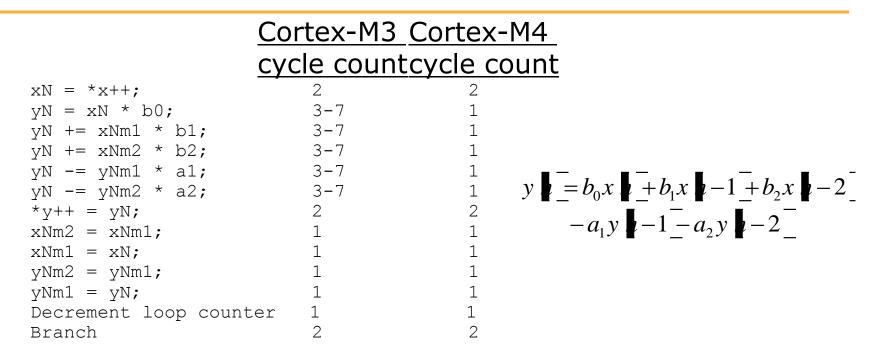

## IIR – single cycle MAC benefit

- Only looking at the inner loop, making these assumptions

- Function operates on a block of samples

- Coefficients b0, b1, b2, a1, and a2 are in registers

- Previous states, x[n-1], x[n-2], y[n-1], and y[n-2] are in registers

- Inner loop on Cortex-M3 takes 27-47 cycles per sample

- Inner loop on Cortex-M4 takes 16 cycles per sample

The Architecture for the Digital World®

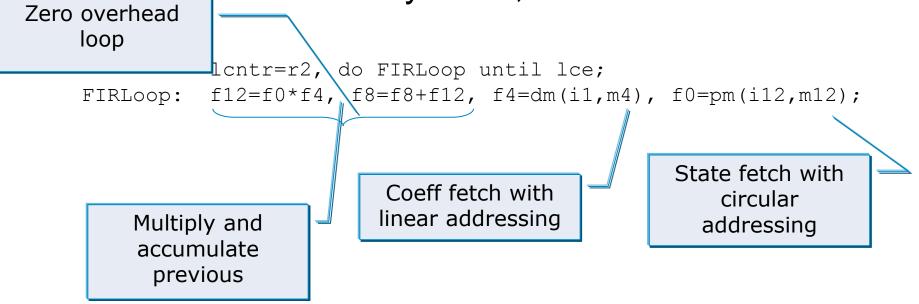

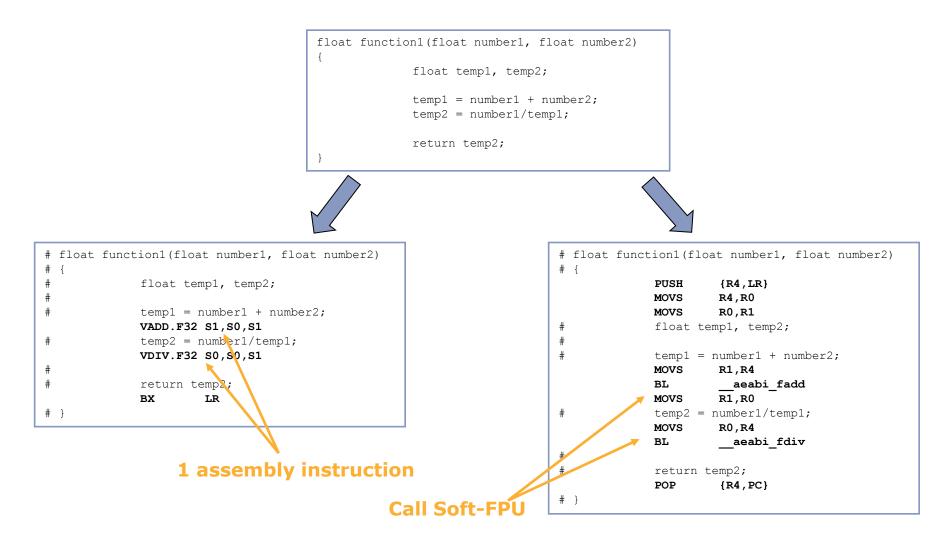

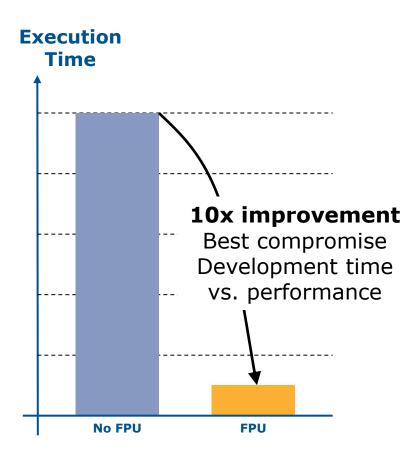

# **Further optimization strategies**

- Circular addressing alternatives

- Loop unrolling

- Caching of intermediate variables

- Extensive use of SIMD and intrinsics

The Architecture for the Digital World®

# FIR Filter Standard C Code

```

void fir(q31 t *in, q31 t *out, q31 t *coeffs, int *stateIndexPtr,

int filtLen, int blockSize)

int sample;

int k;

q31 t sum;